## VISHAWKARMA SCIENTIFIC WORKS AN ISO 9001: 2015 Certified Company

AN ISO 9001: 2015 Certified Company

761, Dina Mandi, Ambala Cantt website: www.viskawmeters.co.in

contact: +91 9953241920, 8882030155 Email- viskawmeters@gmail.com

(LAB MANUAL)

BREAD BOARDS AND IC

### Index

| onter | tts                                                                                         | 10 NO. |

|-------|---------------------------------------------------------------------------------------------|--------|

|       | Features                                                                                    | 2      |

| 2.    | Standard Accessories                                                                        | 2-3    |

| 3.    | Experiment 1: Study of OR, AND, NOT, NAND, NOR, EX-OR GATES and verification                |        |

| ^     | of their truth tables.                                                                      | 3-6    |

| 5.    | Experiment 2:To study the Boolean Algebraic Theorems.                                       | 6-13   |

| 6.    | Experiment 3:Study and verification of truth tables of digital adders and subtractors.      | 13-15  |

| 7.    | Experiment 4: Study of Code Converters.                                                     | 15-16  |

| 8.    | Experiment 5: Study and verification of truth tables of comparators.                        | 16     |

| 9.    | Experiment 6: Study of flip flops and verification of their truth tables.                   | 17-19  |

| 10.   | Experiment 7: Study of Counters & Shift Registers and verification of their truth tables.   | 19-24  |

| 11.   | Experiment 8: Study of Encoders & Decoders and verification of their truth tables.          | 24-25  |

| 12.   | Experiment 9: Study of Multiplexers, Demultiplexers and verification of their truth tables. | 26-27  |

| 13.   | Experiment 10 :To Conduct CMOS to TTL IC and TTL to CMOS IC Interfacing                     | 28-30  |

| 13.   | Experiment using pull up resistors and transistors.                                         |        |

| 14.   | Pin description of all logic IC's.                                                          | 31     |

### instruction Manual

### For

### Digital IC Circuit Trainer

Digital IC Circuit Trainer offers a unique entry into the world of digital electronics.

The system combines simple, easy to use, IC's for GATES, arithmatic operations flip-flops, power supply, input and outpu states with a versatile solderless bread board.

Students know how digital electronics can implement logic circuit in a matter of seconds on the bread board.

This unique approach enables the unit to be used by the absolute beginner. Yet it may also be usefully employed in advanced project work.

### **Features**

### DC Regulated Power Supplies

: One fixed DC regulated power supply of 5V/1Amp 1. Output voltages

One fixed output DC regulated power supply of ±15V/ 500mA

2. Load regulation : + 0.2% 3. Line regulation : + 0.05%

: Less than 3mV RMS 4. Ripple

: Short circuit & over load protected 5. **Protections**

Power requirement : 230 VAC +10%, 50 Hz 6.

: 3.5 Digit Dual range (2V/20V) 7. Voltmeter

### Logic Input/Output

Inbuilt 10 logic inputs, logic '0' & logic '1' selectable using SPDT switches, 10 logic output indicators. 8.

1Hz monoshot clock pulse, automatic clock pulse generator having clock pulses output 1Hz, 1KHz, & 10KHz 9. selectable through band switch

Seven Segment display with seven I/P terminals for seven logic inputs. 10.

### **Bread Board Strips**

2 Nos vertically common strips (640 Tie points each) 10.

4 Nos horizontally common strips(100 Tie points each) 11.

### STANDARD ACCESSORIES

The following integrated circuits & patchcords are supplied with the logic computer.

| 4        | 7400  | ٠. | Quad 2 input NAND GATE.     | 2.  | 7402  | : | Quad 2 input NOR GATE.     |

|----------|-------|----|-----------------------------|-----|-------|---|----------------------------|

| 1.<br>3. | 7404  | :  | Hex invertor.               | 4.  | 7408  | ; | Quad 2 input AND GATE.     |

| 5.       | 7411  |    | Triple - 3 input AND GATES. | 6.  | 7420  | : | 4 input NAND GATE.         |

| 7.       | 7427  |    | TIL SITUAL NOR CATES        | 8.  | 7430  | : | 8 - input NAND GATE.       |

| 9.       | 7432  |    | O LOS CATE                  | 10. | 7442  | : | BCD to Decimal Decoder.    |

| 11.      | 7447  | :  | BCD to 7-Segment Decoder.   | 12. | 7472  | : | AND- GATES JK Flip-Flop.   |

| 13.      | 7474  | :  | Dual D type Flip Flops      | 14. | 7476  | : | Dual JK Flip Flops (2Pcs.) |

| 15.      | 7486  |    | Quad exclusive - OR GATE.   | 16. | 7490  | : | Decade Counter.            |

| 17.      | 7495  |    | Shift Register.             | 18. | 74153 | : | 1 to 4 line Demultiplexer. |

| 19.      | 74155 | :  | 4 to 1 line Multiplexer.    | 20. | 74193 | : | Synchronous Counter.       |

|          |       |    |                             |     |       |   |                            |

Hook up wire 5 mt. suitable for Bread Board. 21.

Eighteen Patchcords with 4 mm Plug on single side. 22.

### **Experiments to be Performed**

- Study of OR, AND, NOT, NAND, NOR, EX-OR Gates & Vertification of their truth tables.

- Verification of Boolean Identities & Demorgan's theorems.

- 3. Study & Verification of truth tables of Digital Adders & Subtractors .

- Study and verification of truth tables of comparators.

- 5. Study of code converters i.e. binary to gray, gray to binary code

- Study of flip flops and verification of their truth tables.

- Study of Counters & Shift Registers, memory register and verification of their truth tables.

- Study of Encoders & Decoders and verification of their truth tables.

- Study of Multiplexers, Demultiplexers and verification of their truth tables.

- Study of TTL-CMOS & CMOS-TTL Interfacing.

### Experiment 1:-

Study of OR, AND, NOT, NAND, NOR, EX-OR GATES and verification of their truth tables.

NOTE:- Pin description of all logic IC's are given on Page No. 40.

### **Theory**

All the digital equipment simple or complex are derived from just a ten basic circuits, called logic elements. There are two basic types of digital logic circuits i.e. "decision making" and "memory". Decision making elements monitor the binary inputs and produce outputs based on the inputs state and operational characteristics of the logic element. Memory elements are used to store binary data's. The decision making circuits are called 'GATES' while the memory circuits are made up and called 'Flip-Flop.'

The GATES are logic circuits & act as an ON/OFF switch also. The GATE shows either ON (HIGH) or OFF (LOW) state in the digital electronics. There are three basic decision making elements of gates i.e. OR, AND and NOT (INVERTER). From these three operations, two more operations have been derived, the NAND operation and the NOR operation. These operations have become very popular and are widely used, the reason being thay only one type of gates, no. of NAND & NOR GATES are sufficient for the realization of any logical expression. Because of this reason, NAND and NOR GATES are known as universal GATES.

A GATE is a circuit with one output and two or more input channels, an output signal occurs only for certain combinations of input signals. Logic circuits are used to perform various computer functions.

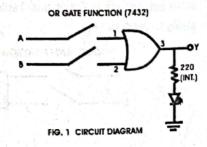

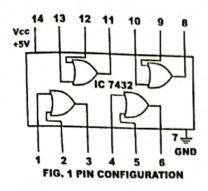

### Verification of 'OR' GATE:

'OR' GATE can have two or more inputs and signal output. It is defined as whenever anyone or all the input are high then output must be high otherwise output is low. For 2-input 'OR' GATE we are using IC 7432, Pin configuration, Circuit diagram and truth table are shown in fig. 1, and table 1 respectively. Mathematically

it is expressed as Y = A+B

(Y equals A or B).

Page 3/31 Rev. 02

### Procedure :-

- Put the IC in lower bread board and connect 5volts DC supply from pin No. 30 and ground .

pin No. 35 of upper bread board meant for connections.

- 2. Give input signal to logic GATE from pin no. 13,17, 21or 25 of upper bread board.

- Connect output of GATE to LED indicator pin no. 40, 46, 52 or 58 of upper, bread board.

- Connect the mains lead to 230 VAC and throw the power switch to 'ON' position.

The jewel light will glow indicating that the trainer is ready for use.

- Give the HIGH or LOW singals from debunced logic switch and observe the output (1 or 0) by (ON or OFF) indicator.

- Verify the truth table as given in Table 1.

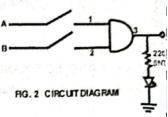

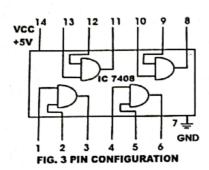

### Verification of 'AND' GATE :-

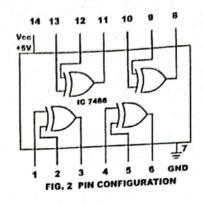

'AND' GATE can have two or more inputs and a single output. It is defined as when all the inputs are high then output must be high otherwise output is low. For a 2 - inputs 'AND' GATE using IC 7408. Pin configuration, circuit diagram and truth table symbol are shown in Fig. 2 and table 2 respectively. Mathematically it is expressed as Y=A.B (Y equals A and B).

### Procedure

Make the circuit of Fig. (2) and follow procedure of Experiment No.

1. Verify the truth table as given in Table 2.

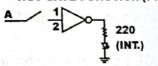

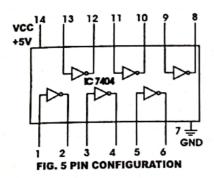

### Verification of 'NOT' GATE:-

The simplest from of logic circuit is the INVERTER or NOT GATE. It has one input and one output terminal. It is defined as whenever input is high then output is low and vice-versa or we can say that the inverter is a logic element whose output state is always opposite of its input state. For that function we are using IC 7404. Pin configuration, circuit diagram and truth table are shown in Fig. 3 and Table 3. Mathematically it is expresses as Y =

### Procedure :-

Make the circuit of Fig. 3 and follow procedure of Experiment No. 1. Verify the truth table as given in Table 3.

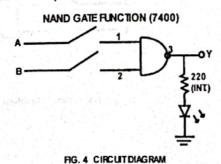

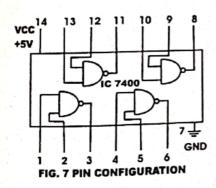

### Verification of 'NAND' GATE :-

A (read as Y euals A NOT).

The term 'NAND' is a contraction of the expression NOT - AND. A 'NAND' GATE therefore, is 'AND' GATE followed by an inverter. It is defined as

whenever all the inputs are high then output must be low otherwise output is high. For 2 - inputs 'NAND' GATE we are using IC 7400. Pin configuration, circuit diagram and truth table are shown in Fig. 4 and Table 4. Mathematically it is expressed as Y = A.B ( Y = A.B)

euals A nad B NOT).

|   | (UTIT TABLE | _  |

|---|-------------|----|

| Α | В           | Υ  |

| 0 | 0           | 0  |

| 0 | 1           | 1  |

| 1 | 0           | 1  |

| 1 | 1           | _1 |

POSITIVE LOGIC

AND GATE PUNCTION (7408)

TRUTH TABLE - 2

| Α | В   | Υ   |

|---|-----|-----|

| 0 | 0   | 0   |

| 0 | 4   | . 0 |

| 1 | 0   | 0   |

| 1 | 1.1 | 1   |

**POSITIVE LOGIC**

$$Y = AB$$

### **NOT GATE FUNCTION (7404)**

FIG. 3 CIRCUIT DIAGRAM

### TRUTH TABLE - 3

| A | Y |  |  |

|---|---|--|--|

| 0 | 1 |  |  |

| 1 | 0 |  |  |

POSITIVE LOGIC

$$Y = A$$

**POSITIVE LOGIC**

Y = AB

Page 4/.

### Procedure :-

Make the circuit of Fig. 4. and follow procedure of Experiment No. 1. Verify the truth table as given in Table 4.

# NOR GATE FUNCTION (7402) 3 220 FIG. 5 CIRCUIT DIAGRAM

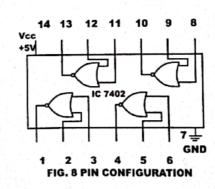

### Verification of 'NOR' GATE :-

The 'NOR' GATE is an improved logic element used for implementing decision making logic functions. The term 'NOR' is a contraction for the expression 'NOT' 'OR'. The 'NOR' GATE is essentially a circuit containing the logic function of an 'OR' GATE and inverter. For 2 - inputs 'NOR' GATE we are using IC 7402. Pin cinfiguration diagram and truth table are shown in Fig. 5 and Table 5. It is defined as whenever all the inputs are low then output must be high otherwise output is low.

### Procedure:-

Make the circuit of Fig. 5 and follow procedure of Experiment No. 1. Verify the truth table as given in 5

### TRUTH TABLE - 5

| A   | В      | Y |

|-----|--------|---|

| 0   | 0      | 1 |

| 0   | 1      | 0 |

| 1   | 0      | 0 |

| 110 | 103100 | 0 |

**POSITIVE LOGIC**

Y = A + B

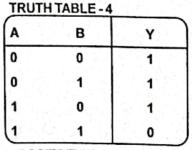

### Verification of 'EX-OR' GATE :-

The 'Exclusive-OR' (EX-OR) operation is widely used in digital circuits. It is not a basic operation and can be performed using the basic gates. 'AND', 'OR' and 'NOT' or universal GATES 'NAND' or 'NOR'. It is similar to the basic 'OR' GATE expect that the output is low when both the inputs are high and low. The output of the gate is high when anyone output is high. For 2 - inputs 'EX-OR' GATE we are using IC 7486. Pin configuration, circuit diagram and truth table are shown in Fig. 6 and Table 6. 'Exclusive-OR' (EX-OR) circuits are used in applications like adder substraction, parity checkers etc. Mathematically expression of 'EX-OR' is given by Y = AB + AB.

FIG .6 CIRCUIT DIAGRAM

### Procedure:-

Make the circuit of Fig. 6 and follow procedure of Experiment No. 1. Verify the truth table as given in Fig. 6.

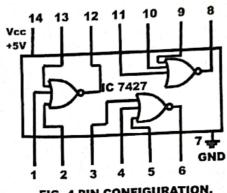

### Verification of 3 - Input 'NOR' GATE :-

It is defined as whenever all the input are low then output must be high otherwise output is low. For 3 - inputs 'NOR' GATE we are using IC 7427. Pin configuration, circuit diagram and truth table are shown in Fig. 7 and Table 7.

| TRUTH TABLE -        | 6 |

|----------------------|---|

| A B                  | Y |

| 0                    | 0 |

| 0.0 1                | 1 |

| udal-Celo Orranol    | 1 |

| 8411-1 06014 (841.2) | 0 |

| POSITIVE LOGIC       |   |

Y = AB + BA

### **Procedure**

Make the cicuit of Fig. 7 and follow the procedure of Experiment no. 1 and verify the truth table as given in Table 7.

PROBE TELEPROPERTY TO THE AST INC. IN.

| NOR GATE FUNCTION ( 742     | <b>7)</b><br>Francos |

|-----------------------------|----------------------|

| 2 1                         | 2Y                   |

| 77 10 Educa 1 13 1 1900 E   | ₹220<br>₹(INT.)      |

| FIG. 7 CIRCUIT DIAGRAM      | 4                    |

| Lawren Charles of the beans | ± Environment        |

| Α | Bying C | mar Y   |

|---|---------|---------|

| 0 | 00      | tot est |

| 0 | 0 vs 1  | 0       |

|   | 1 1 0   |         |

| _ | 1 11    |         |

|   | 0 0     | 0       |

| 1 | 0 1     | 0       |

| 4 | 1 0     | 0       |

| 1 | 1 1     | . 0     |

**POSITIVE LOGIC**

Y = A+B+C

Page 5/31 Rev. 02

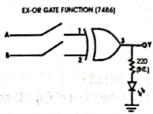

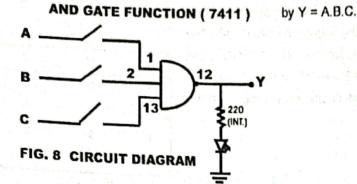

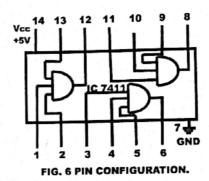

### Verification of 3 - Input 'AND' GATE :-

It is defined as when all the input high then output must be high otherwise output is low. For 3 input 'AND' GATE We a using IC 7411. Pin configuration, circuit diagram and truth.

table are shown in Fig. 8 and Table 8. It is mathematically expresse

|   | IKOTH TABLE - 8 |      |       |  |  |

|---|-----------------|------|-------|--|--|

| A | В               | С    | V     |  |  |

| 0 | 0               | 0    | -     |  |  |

| 0 | 0               | 1    | 0     |  |  |

| 0 | 1               | 0    | 0     |  |  |

| 0 | 1               | 1    | 0     |  |  |

| 1 | 0               | 0    | 0     |  |  |

| 1 | 0               | 1    | 0     |  |  |

| 1 | 1               | 0    | 0     |  |  |

| 1 | 1               | 1.50 | la la |  |  |

**POSITIVE LOGIC**

Y = A.B.C

### Procedure :-

Make the cicuit of Fig. (8) and follow the procedure of Experiment no. 1 and verify the truth table as given in Table 8. **Experiment 2**: To study the Boolean Algebraic Theorems.

### **Objective**

To familiarise and verify the following Boolean Algebraic Theorems and to simplify and realize the following expression: Integrated Circuit to be used :-

- 1. IC 7404 Hex Inverter (Six, 1 - Input 'NOT' GATES)

- 2. IC 7408 Quad 2 - Input 'AND GATES

OR

IC 7411 Triple 3 - input 'AND' GATES where necessary.

3. IC 7432 Quad 2 - Input "OR' GATES

IC 7427 Triple 3 - input 'NOR' GATES in combination with IC 7404 to make 3 - input 'OR' GATES as follows where necessary.

### Theory

The digital signals are discreate in nature and can only assume one of the two values '0' or '1'. A number system based or these two digits is known as binary number system. In the middle of 19th century, an English mathematician George Boole developed rules for manipulations of binary numbers, known as Boolean Algebra. This is the basis of all digital system like computers, calculators etc.

Binary variables can be represented by a letter symbol such as A, B, X, Y, ....... The variable can have only one of the two positive values at any time, viz, '0' or '1'. The Boolean Algebraic Theorems are given in table No. (1).

From these theorems, we observe that the even numbered theorems can be obtained from their preceding odd numbered theorems by (i) interchanging and signs, and (ii) interchanging '0' and '1'. Theorems which are related in this way are called duals. Theorems 1 to 8 involve a single variable only. Each of these theorems can be proved by considering possible value of the variable. Theorema 9 to 20 involve more than one variable and can be proved by making a truth table. Theorems 21 and 22 are known as Demorgan's Theorems. These theorems can be proved by first considering the two variable case and their extending this result. To familiarise and verify the following Boolean Algebric Theorems and to simplify and relize the expression. Page 6/31

Rev. C

### Theorm - 1 :- A + O=A

### Procedure :-

- Make the circuit as shown in Fig. 9 and connect the inputs of 'OR' GATE, to the two input state sockets 'A' & 'B' and output of 'OR' GATE to the output indicator socket T<sub>1</sub> for LED L<sub>1</sub>.

- OUTPUT 0R 0UTPUT 22200 FIG. (9)

- 2. Set the input combinations by putting input state switches either '0' or '1' state. Input state switch of 'B' always should be zero and 'A' input state switch either '0' or '1' state.

- 3. Now verify the output, if input state switch of 'A' in '0' state. Output indicator LED L<sub>1</sub> should be 'OFF'. If 'A' in '1' state, then LED L<sub>1</sub> should be 'ON'. Hence the theorem is proved.

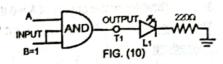

### Theorem - 2:- A . 1 = A

### Procedure :-

- Make the circuit as shown in Fig. 10 and connect the inputs of the 'AND' GATE, to the two input state sockets 'A'

& 'B' and output to the output indicator socket T<sub>1</sub> for LED L<sub>1</sub>.

- 2. Put input state switch 'B' always in '1' state and switch 'A' either in '0' or

- Now verify the output. If B = 1 & A = 0, indicator LED L<sub>1</sub> should be 'OFF' and if A = 1 then LED L<sub>1</sub> Should be 'ON'. Hence the theorem is proved.

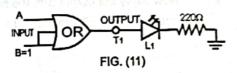

### Theorem - 3: - A + 1 = 1 having stay's harm select B

### Procedure:-

- 1. Make the circuit as shown in Fig. 11 and connect the inputs of 'OR' GATE, to the two input state sockets 'A' & 'B' and output to the output indicator socket T<sub>1</sub> for LED L<sub>1</sub>.

- 2. Put input state switch 'B' always in '1' state and switch 'A' either in '0' or '1' state.

- Now verify the output. If B = 1 & A = 0 or 1 then indicator LED L<sub>1</sub> should be continuously 'ON'. Hence the theorem is proved.

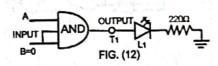

### Theorem -4: - A . 0 = 0

### Procedure:-

- Make the circuit as shown in Fig. 12 and connect the inputs of 'AND' GATE, to the two input state sockets 'A' &

'B' and output to the output indicator socket T<sub>1</sub> for LED L<sub>1</sub>.

- Put input state switch 'B' always in '0' state and switch 'A' either in '0' or

'1' state.

- Now verify the output. If B = 0 & A = 0 or 1 then indicator LED L<sub>1</sub> should be continuously 'OFF'. Hence the theorem is proved.

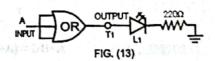

### $\underline{\text{Theorem - 5}} :- A + A = A$

### Procedure :-

1. Make the circuit as shown in Fig. 13 and connect the inputs of 'OR' AND GATE, to the input state sockets 'A' and output to the output indicator socket T<sub>1</sub> for LED L<sub>1</sub>.

- 2. Put input state switch 'A' always either in '0' or '1' state.

- 3. Now verify the output. If A = 1 then indicator LED L<sub>1</sub> should be continuously 'ON' and if A = 0 then indicator LED L<sub>1</sub> should be 'OFF'. Hence the theorem is proved.

### <u>Theorem - 6</u> :- A.A = A

### Procedure :-

- Make the circuit as shown in Fig. 14 and connect the inputs of 'AND' GATE, to the input state sockets 'A' and output to the output indicator socket T<sub>1</sub> for LED L<sub>1</sub>.

- 2. Put input state switch 'A' in '0' or '1' state.

- Now verify the output. If A = 0, output indicator LED L<sub>1</sub> should be 'OFF' and if A = 1 should be 'ON'. Hence the theorem is proved.

Page 7/31 Rev. 02

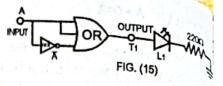

### Theorem - 7 :-

Procedure :-

Make the circuit as shown in Fig. 15 and connect the inputs of the GATE, to the input state sockets 'A' and output to the output indicator socket T, for LED L,

- 2. Put input state switch 'A' either in '0' or '1' state.

- Now verify the output. If A = 1 or 0, output indicator LED L<sub>1</sub> should be continuously 'ON'. Hence the theorem 3. proved.

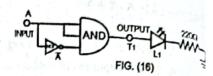

Theorem - 8 :- A . A = 0

Procedure :-

1. Make the circuit as shown in Fig. 16 and connect the GATE, to the input state sockets 'A' and output to the output indicator socket T, for LED L.

- 2. Put input state switch 'A' either in '0' or '1' state.

- Now verify the output. If A = 0 then indicator LED  $L_1$  should be continuously 'OFF'. Hence the theorem is prove. 3.

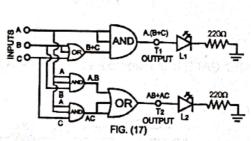

Theorem - 9: - A. (B + C) = AB + AC

Procedure :-

- Make the circuit as shown in Fig. 17 and connect the GATE, to the input state sockets 'A', 'B' & 'C' and output 1. the output indicator socket  $T_1$  for LED  $L_1$  and  $T_2$  for LED  $L_2$ .

- Set the input combinations one by one by putting input state switches 'A', 'B' & 'C' either in '0' or '1' state. (A 2. shown in Truth Table No.9).

- Now verify the output with the help of Truth Table No. 9. Output indicator LED L1 & L2 should be 'OFF' or 'O 3. according to the Truth Table No. 9. Hence the theorem is proved.

| _    |     | TRUTH TABLE -9 |     |     |               | E-9 |     |         |  |

|------|-----|----------------|-----|-----|---------------|-----|-----|---------|--|

| L    | Α   | В              | С   | B+C | A.(B+C)       | A.B | A.C | (AB+AC) |  |

|      | 0   | 0              | 0   | 0   | 0             | 0   | 0   | 0       |  |

|      | 0   | 0              | 1   | 1   | 0             | 0   | 0   | 0       |  |

|      | 0   | 1              | 0   | 1   | 0             | 0   | 0   | 0       |  |

| ) In | 0 🔨 | 1.             | 110 | 1   | 0             |     | 0   | 0       |  |

|      | 1   | 0              | 0   | 0   | 0             | 0   | 0   | 0       |  |

| + (1 | 1   | 0              | 1   | 1 1 | A 2 0 7 5 1 A | 0   | 11  | 1       |  |

|      | 1   | 1              | 0   | 1   | ree fores     | 1   | 0   | 1       |  |

|      | 1   | 1              | 1   | 1   | 1             | 414 | 1   | 1       |  |

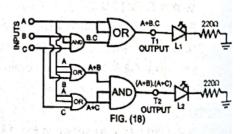

A+BC = (A+B).(A+C) Theorem - 10:-

Procedure :-

- 1. Make the circuit as shown in Fig. 18 and connect the GATE, to the inputs of the GATE to the input state sockets 'A', 'B' & 'C' and output to the output indicator socket T, for LED L, and T, for LED

- Set the input combinations one by one by putting input state 2. switches 'A', 'B' & 'C' either in '0' or '1' state. (As shown in Truth

Now verify the output with the help of Truth Table No. 3. Output indicator LED L, & L2 should be 'ON' or 'OFF' by input combinations according to the Truth Table No. 3, so it is proved that A+BC = (A+B). (A+C).

Page 8/31 Rev. 02

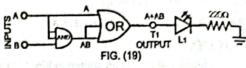

### rocedure:-

- Make the circuit as shown in Fig. (19) and connect the inputs of the GATE to the input state sockets 'A' & 'B' and output to the output indicator socket T, for LED L.

- Put the input state switches 'A' in '1' 2. state and 'B' either in '0' or '1' state.

- Now verify the output with the help of Truth 3. Table No.11. If 'A' = '1' and 'B' = '0' or '1', the output indicator LED L, should be 'ON'.

| Α  | В   | С   | B.C | A+B.C | A+B | A+C | (A+B).(A+C) |

|----|-----|-----|-----|-------|-----|-----|-------------|

| 0  | 0   | 0   | 0   | 0     | 0   | 0   | 0           |

| 0  | 0   | 1   | 0   | 0     | 0   | 1   | 0           |

| 0  | 1   | 0   | 0   | 0     | 1   | 0   | 0           |

| 0  | 1.  | 1   | . 1 | 1     | . 1 | . 1 | 5 man 1     |

| 1  | 0   | 0   | . 0 | 1.    | 1   | 1   | 1           |

| 1  | . 0 | . 1 | 0   | 1     | 1   | 1.  | 1           |

| 1  | 1   | 0   | 0   | 1     | 1   | 1   | 1           |

| 40 | 1   | 101 | 19  | 1     | 11  | 1   | 1           |

TRUTH TARLE - 10

Now verify the output also if 'A' = '0' and 'B' = '0' or '1', the output 4. indicator LED L, should be 'OFF'. In this way the theorem is proved.

### Theorem - 12: A.(A+B) = A

### Procedure:-

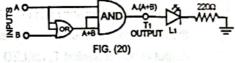

- Make the circuit as shown in Fig. (20) and connect the inputs of the GATE to the input state sockets 'A' & 'B' and output, to the output indicator socket T, for LED L,

- Put the input state switches 'A' always in '1' or '0' state and evolve 2. switch.

'B' either in 'o' or '1' state.

Now verify the output with the help of Truth Table No. 12. The output indicator LED L, should be 'ON' or 'OFF' by input combinations. Hence the theorem is proved.

## TRUTH TABLE - 11

|   | A     | В       | AB | A+AB    |

|---|-------|---------|----|---------|

|   | 0     | 0       | 0  | 0       |

| , | 0     | 1 6     | 0  | 0       |

| ¢ | 1     | 0       | 0  | . 1     |

|   | 91197 | so 1 () | 1  | 1°, 1°, |

## FIG. (20)

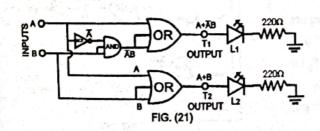

### A+AB = (A+B)Theorem - 13:-

### Procedure:-

- Make the circuit as shown in Fig. 21 and connect the inputs of the GATE to the input state sockets 'A' & 'B' and output to the output indicator socket T, for LED L, and T2 for LED L2.

- Set the input combinations one by one by putting input state switches 2. 'A' & 'B' either in '0' or '1' state.

- 3. Now verify the output with the help of Truth Table No. 13. The output indicator LED's L, & L2 should be 'OFF' or 'ON' by input combinations, so it is proved that A+AB = A+B.

### TRUTH TABLE - 12

| Α.             | В | A+B | A.(A+B) | 1 |

|----------------|---|-----|---------|---|

| ( <b>( 0</b> ) | 0 | 0   | top: 0  |   |

| 0              | 1 | 1.  | 0       |   |

| 1              | 0 |     | 1.      |   |

| 1              | 1 | 1.  | 1       |   |

| TRU | THI | <b>TABL</b> | E-13 |

|-----|-----|-------------|------|

|-----|-----|-------------|------|

| ( A   | lge.       | В   | Ā     | ĀB | A+ĀB      | A+B |

|-------|------------|-----|-------|----|-----------|-----|

| , / 0 | e je       | 0   | pudo: |    | 0         | 0   |

| 0     | ele<br>sul | 110 | 40    | 1  | 4.11      | 1   |

| 1     |            | 0   | 0     | 0  | 1         | 1   |

| 1     | e de la    | 1   | 0     | 0  | iles jugi | 1   |

Page 9/31 Rev. 02

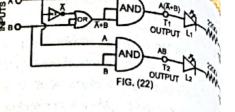

### Theorem - 14:- $A.(\overline{A}+B) = AB$

### Procedure :-

Make the circuit as shown in Fig. 22 and connect the inputs of the GATE to the input state sockets 'A' & 'B' and output to the output indicator socket T, for LED L, and T, for LED L,

Set the input combinations one by one by putting input state 2. switches 'A' & 'B' either in '0' or '1' state.

3. Now verify the output with the help of Truth Table No. 14. Then output indicator LED L, & L<sub>2</sub> should be 'ON' or 'OFF' by input combinations. Hence the

|   |     | TRUT | HTABLE | -14   |

|---|-----|------|--------|-------|

| A | В   | Ā    |        | A.(Ā+ |

| 0 | 0   | 1    | 1.     | 0     |

| 0 | . 1 | 1 /  | 1      | 0     |

| 1 | 0   | 0    | 0      | 0     |

## FIG. (23)

TRUTH TABLE - 15

### Theorem - 15 :-AB+AB = A Procedure:

theorem is proved.

- 1. Make the circuit as shown in Fig. (23) and connect the inputs of the GATE to the input state sockets 'A' & 'B' and output to the output indicator socket T, for . LED L.

- 2. Set the input combinations one by one by putting input state switches 'A' & 'B' either in '0' or '1' state.

- 3. Now verify the output with the help of Truth Table No. 15. The output indicator LED L, should be 'ON' or 'OFF' by input combinations. Hence the theorem is proved.

### Theorem - 16: $(A+B).(A+\overline{B}) = A$

### Procedure :-

- 1. Make the circuit as shown in Fig. (24) and connect the inputs of the GATE to the input state sockets 'A' & 'B' and output to the output indicator socket T, for LED L,.

- 2. Set the input combinations one by one by putting input state

input combinations. Hence the theorem is proved.

switches 'A' & 'B' either in '0' or '1' state. 3.

$\overline{\mathbf{B}}$ AB  $\overline{AB}$ B AB+AP 0 1 0 0 Λ 1 0 0 0 n 1 0 0 1 1 0 1 1

Now verify the output with the help of Truth Table No. 16. Then output indicator LED L, should be 'ON' or 'OFF' bigget combinations. House the thousand is proved.

TRUTH TABLE - 16

| A0-  |     | A+B           |      |

|------|-----|---------------|------|

| PUTS |     | AND (A+BXA+B) | 220Ω |

| N.   | 400 | OUTPUT L      | ¬₩,ੌ |

| во   |     | A+B FIG. (24) |      |

| A   | В   | В                  | A+B           | A+B     | (A+B).(A+B) |

|-----|-----|--------------------|---------------|---------|-------------|

| 0   | . 0 | A : <b>1</b> : p : | 0<br>.1<br>.1 | 1       | 0           |

| 0   | 1   | 0                  | a 1 by        | 0       | 0           |

| 1   | 0   | 1                  | 10            | who the | 1           |

| 114 | 1   | 0                  | 19.0          | 1       | 1           |

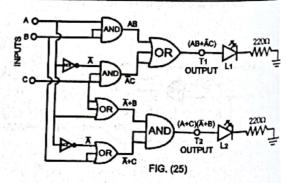

### Theorem - 17: $AB+\overline{A}C = (A+C).(\overline{A}+B)$

Truth Table - 17.

### Procedure:-

- Make the circuit as shown in Fig. (25) and connect the inputs 1. of the GATE to the input state sockets 'A', 'B' & 'C' and output to the output indicator socket T, for LED L, and T2 for LED L2.

- Set the input combina -tions one by one by putting input 2. switches 'A', 'B' & 'C' either in '0' or '1' state according to

Page 10/31 Rev. 02

Now verify the output with the help of Truth Table No. 10. The output indicator LED L<sub>1</sub> & L<sub>2</sub> should be 'OFF' or 'ON'

by input combinations. Hence the theorem is proved.

| • | 71 | • | ٠. |    |   | _   |     | • |

|---|----|---|----|----|---|-----|-----|---|

|   | ΝI |   | м  | 10 | м | LE. | . 1 | , |

|   |    |   |    |    |   |     |     |   |

| A | В   | С | Ā   | AB | ĀC | AB+ÃC | A+C | Ā+B | (A+C).(Ā+B) |

|---|-----|---|-----|----|----|-------|-----|-----|-------------|

| 0 | 0   | 0 | 1   | 0  | 0  | 0     | 0   | 1   | 0           |

| 0 | 0   | 1 | 1 j | 0  | 1. | 1     | 1   | 1   | 1           |

| 0 | 1   | 0 | 1   | 0  | 0  | 0     | 0   | 1   | 0           |

| 0 | 1 5 | 1 | 1   | 0  | 1  | 1     | 1   | 1   | 1           |

| 1 | 0   | 0 | 0   | 0  | 0  | 0     | 1   | 0   | 0           |

| 1 | 0   | 1 | 0   | 0  | 0  | 0     | 1   | 0   | 0           |

| 1 | 1   | 0 | 0   | 1  | 0  | 1     | 1   | 1   | 1 .         |

| 1 | 1   | 1 | 0   | 1  | 0  | 1     | 1   | . 1 | . 1         |

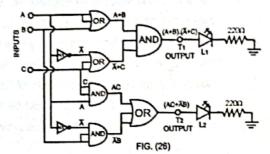

### Theorem - 18: $(A+B).(\overline{A}+C) = AC+\overline{A}B$

### Procedure:-

- Make the circuit as shown in Fig. (26) and connect the inputs of the GATE to the input state sockets 'A', 'B' & 'C' and output to the output indicator socket T<sub>1</sub> for LED L<sub>1</sub> and T<sub>2</sub> for LED L<sub>2</sub>.

- Set the input combinations one by one by putting input state switches 'A', 'B' & 'C' either in '0' or '1' state according to Truth Table - 18.

Now verify the output with the help of Truth Table No. 11. The output indicator LED L<sub>1</sub> & L<sub>2</sub> should be 'ON' or 'OFF' by input combinations. Hence the theorem is proved.

TRUTH TABLE - 18

| A    | В | С | Ā  | A+B | Ā+C | (A+B).(A+C)    | AC              | ĀB | AC+AB     |

|------|---|---|----|-----|-----|----------------|-----------------|----|-----------|

| 0    | 0 | 0 | 1. | 0   | 1   | 0              | 0               | 0  | 0         |

| 0    | 0 | 1 | 1  | 0   | 1   | 0              | 0               | 0  | 0         |

| 0    | 1 | 0 | 1  | 1   | 1   | 1.             | 0               | 1  | 1         |

| 0    | 1 | 1 | 1  | 1   | 1   | 11             | 0               | 1  | 1 1       |

| 1    | 0 | 0 | 0  | 1   | 0   | 0              | 0               | 0  | 0         |

| 1    | 0 | 1 | 0  | 11  | 400 | A TOTAL CONTRA | seri <b>1</b> a | 0  | 361.1     |

| 1    | 1 | 0 | 0  | 1   | 0   | 0              | 0               | 0  | 0         |

| 83.1 | 1 | 1 | 0  | 1   | 1   | photophas (s)  | 1               | 0  | SE SE TEN |

### Theorem - 19: AB+AC+BC = AB+AC

### Procedure:

- Make the circuit as shown in Fig. (27) and connect the inputs of the GATE to the input state sockets 'A', 'B' & 'C' and output to the output indicator socket T<sub>1</sub> for LED L<sub>1</sub> and T<sub>2</sub> for LED L<sub>2</sub>.

- 2. Set the input combinations one by one by putting input state switches 'A', 'B' & 'C' either in '0' or '1' state.

- Now verify the output with the help of Truth Table No. 19. The output indicator LED L<sub>1</sub>

& L<sub>2</sub> should be 'ON' or 'OFF' by input combinations. Hence the theorem is proved.

Page 11/31 Rev. 02

| E POPULATION OF THE PROPERTY O |                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| \$ 10 MO NO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | OR OUTPUT         |

| CO L AND BO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

| E AND A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OR (MI-AC) (2703) |

| CO C AND A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FIG. (27)         |

| Α | В | C | X | AB | <b>AC</b> | ВС | (AB+AC+BC)(A |

|---|---|---|---|----|-----------|----|--------------|

| 0 | 0 | 0 | 1 | 0  | 0         | 0  | 0            |

| 0 | 0 | 1 | 1 | 0  | 1         | 0  | 1            |

| 0 | 1 | 0 | 1 | 0  | 0         | 0  | 0            |

| 0 | 1 | 1 | 1 | 0  | 1         | 1  | 1            |

| 1 | 0 | 0 | 0 | 0  | 0         | 0  | 0            |

| 1 | 0 | 1 | 0 | 0  | 0         | 0  | 0            |

| 1 | 1 | 0 | 0 | 1  | 0         | 0  | 1            |

| 1 | 1 | 1 | 0 | 1  | 0         | 1  | 1            |

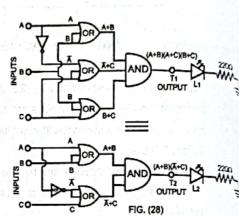

<u>Theorem - 20</u>:- (A+B).(A+C).(B+C) = (A+B).(A+C)

- Make the circuit as shown in Fig. (28) and connect the inputs of the gate to the input state sockets 'A', 'B' & 'C' and output to the output indicator socket T<sub>1</sub> for LED L<sub>1</sub> and T<sub>2</sub> for LED L<sub>2</sub>.

- Set the input combinations one by one by putting input state switches 'A', 'B' & 'C' either in '0' or '1' state.

- Now verify the output with the help of Truth Table No. 20. The output indicator LED L<sub>1</sub> & L<sub>2</sub> should be 'ON' or 'OFF' by input combinations. Hence the theorem is proved.

TRUTH TABLE - 20 Ā C A+B Ā+C B+C (A+B).(A+C).(B+C) (A+B).(A+C) 0 0 0 0 0 0 0 1 0 0 0

<u>Theorem - 21</u>: Demorgan's Theorem - I  $\overline{A.B.C} = \overline{A+B+C}$

### Procedure:-

- Make the circuit as shown in Fig. (29) and connect the inputs of the GATE to the input state sockets 'A', 'B' & 'C' and output to the output indicator socket T<sub>1</sub> for LED L<sub>2</sub> and T<sub>2</sub> for LED L<sub>3</sub>.

- 2 Set the following input combinations one by one by putting input state switches 'A', 'B' & 'C' either in '0' or '1' state.

- AND ABC ABC. 2200 OUTPUT L1 2200 OUTPUT FIG. (29)

- 3. Now verify the output with the help of Truth Table No. 21. The output indicator LED L<sub>1</sub> & L<sub>2</sub> should be 'OFF' or 'Oh by input combinations. So it is proved that A.B.C = A+B+C.

Page 12/3 Rev. 0

|   |   | 1 4 |   | TRUTI | H TABI | .E - 21 |     |       |

|---|---|-----|---|-------|--------|---------|-----|-------|

| A | В | С   | Ā | B     | Ċ      | ABC     | ABC | Ā+B+C |

| 0 | 0 | 0   | 1 | 1     | 1      | 0       | 1   | 1     |

| 0 | 0 | 1   | 1 | 1     | 0      | 0       | 1   | 1     |

| 0 | 1 | 0   | 1 | 0     | 1      | 0       | 1   | 1     |

| 0 | 1 | 1   | 1 | 0     | 0      | 0       | 1   | 1     |

| 1 | 0 | 0   | 0 | 1     | 1      | 0       | 1   | 1     |

| 1 | 0 | 1   | 0 | 1     | 0      | 0       | 1   | 1     |

| 1 | 1 | 0   | 0 | 0     | 1      | 0       | 1   | 1     |

| 1 | 1 | 1   | 0 | 0     | 0      | 1       | 0   | 0     |

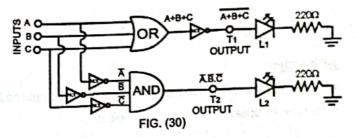

Theorem - 22 : Demorgan's Theorem - II

the BORROW bit.

$\overline{A+B+C} = \overline{A}.\overline{B}.\overline{C}$

### Procedure :-

- Make the circuit as shown in Fig. (30) and connect the inputs of the GATE to the input state sockets 'A', 'B' & 'C' 1. and output to the output indicator socket T, for LED L, and T2 for LED L2.

- Set the input combinations one by one by putting input state switches 'A', 'B' & 'C' either in '0' or '1' state. 2.

- Now verify the output with the help of Truth Table No. 22. The output indicator LED L<sub>1</sub> & L<sub>2</sub> should be 'OFF' or 'ON' 3. by input combinations. So it is proved that A+B+C = A.B.C. of 'B' from, A (i.e, A-B), where 'A' & 'B' are I-bir signals is knows as a Half - Substractor. Its logic gate diagram and truth table are given in Table22. Here 'D' is the DIFFERENCE bit and 'C'

| TD | 117 | ru | T/  | B  | ıE | - 22 | , |

|----|-----|----|-----|----|----|------|---|

| ıĸ | u   | п  | 1 1 | ۱D | ᇆ  | - 44 |   |

|     | IRUII | TIADI | LE - 22 |   |   |       |       |       |

|-----|-------|-------|---------|---|---|-------|-------|-------|

| A   | В     | С     | Ā       | В | c | A+B+C | A+B+C | Ā.B.C |

| 0   | 0     | 0     | 1       | 1 | 1 | 0     | 1     | 1     |

| 0   | 0     | 1010  | 1       | 1 | 0 | 4     | 0     | 0     |

| 0   | 1     | 0     | 1       | 0 | 1 | 1     | 0     | 0     |

| 0   | 1     | 1     | 1       | 0 | 0 | 1     | 0     | 0     |

| 1   | 0     | 0     | 0       | 1 | 1 | 1     | 0     | 0     |

| B14 | 0     | 1     | 0       | 1 | 0 | 1     | 0     | 0     |

| -   | 1     | 0     | 0       | 0 | 1 | 1     | 0     | 0     |

| 1   | 1 1 3 | 1     | 0       | 0 | 0 | 1     | 0     | 0     |

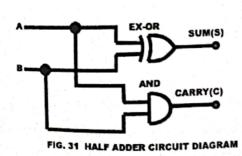

### Experiment- 3 Study and verification of truth tables of digital adders and subtractors.

Set up a half adder according to circuit fig.31 given using EX-OR (7486) & AND (7408) gates & verify the Truth Table 23. **TRUTH TABLE - 23**

| INPL | ITS | OUT | PUT |

|------|-----|-----|-----|

| Α    | В   | S   | C   |

| 0    | 0   | 0   | 0   |

| 0    | 1   | 1   | 0   |

| 1    | 0   | 1   | 0   |

| 1    | 1   | 0   | 1.  |

S=AB+AB C=AB

A Half - Adder has only 2-input terminals and there is no provision to add a carry coming from the lows order bits who binary points and the same an binary numbers are added. For this purpose a third input terminal is added and this circuit is used to-add An Bn & Ch where An & Bn are the nth order bits of the numbers 'A' & 'B' respectively and Cn-1 is the carry generated from addition

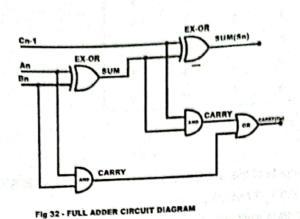

The block diagram of a Full - Adder and its truth table are given in Fig. 32 & Table 24 TRU TRUTH TABLE - 24

OUTPUT INPUT Sn Cn Cn-1 Bn An 0 0 0 0 0 0 1 0 0 0 0 0 0 1 1 0 1 0 0 0 1 0 1 1 0 1 0 1 0 1 1 1 1 1 1

Sn = AnBnCn-1 + AnBnCn-1 +

AnBnCn + AnBnCn-1

Cn=AnBn+BnCn-1+AnCn-1

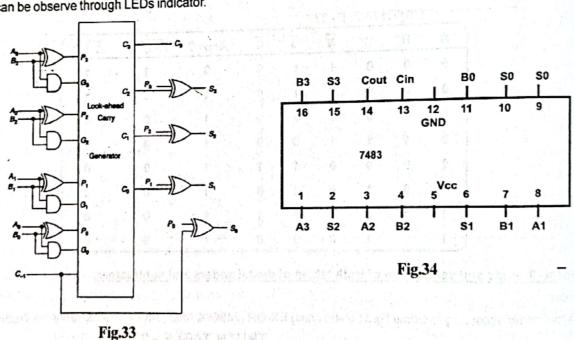

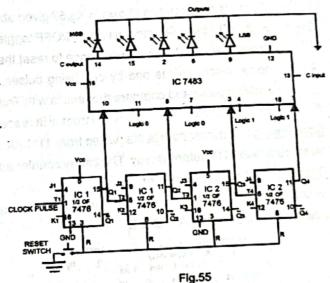

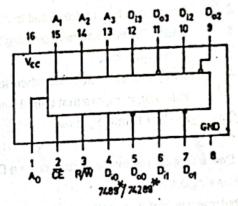

4-bit adder using IC 7483 and verify the two 4 bit data input additions. The pin description of IC 7483 is shown in Fig. 34. output can be observe through LEDs indicator.

Where A3 A2 A1 A0----First 4-bit Data

B3 B2 B1 B0----Second 4-bit Data

S3 S2 S1 S0-----Adder output

Cout----output Carry

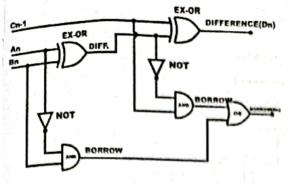

### **Full Subtractor**

Set up Full - Substractor circuit using 7486, 7408, 7432 & 7404 IC's as given in Fig. (35). Verify the truth table experimentally as given in Fig. (25).

Page 14 Rev.

FIR 35 - FULL SUBTRACTOR CIRCUIT DIAGRAM

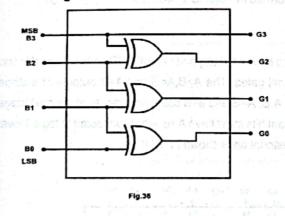

### **Experiment - 4 Study of Code Converters**

### Procedure

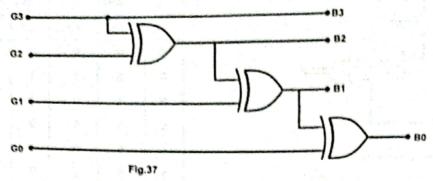

### Binary to Gray Code Converter

Table No.26 shows the Gray Code of 4 Bit Binary Code.

Simplified expression for Gray Code from 4 Bit Binary code using Kmap is

| G3 | = | B3      |

|----|---|---------|

| G2 | = | B2 ⊕ B3 |

G1 =  $B1 \oplus B2$ G0 =  $B0 \oplus B1$

### Procedure

Set up binary to gray code converter using circuit given in figure no. 36. The circuit is using 3 EX-OR gate using IC 7486. Varify the gray code of respective 4 bit binary data.

### Circuit Diagram

### TRUTH TABLE - 25

|    | INPUT | OUT  | PUT |    |

|----|-------|------|-----|----|

| An | Bn    | Cn-1 | Dn  | Bn |

| 0  | 0     | 0    | 0   | 0  |

| 0  | 0     | 1    | 1   | 1  |

| 0  | 1     | 0    | 1   | 1  |

| 0  | 1     | 1    | 0   | 1  |

| 1  | 0     | 0    | 1   | 0  |

| 1  | 0     | 1    | 0   | 0  |

| 1  | 1     | 0    | 0   | 0  |

| 1  | 1     | 1    | 1   | 1  |

Dn = ĀnBnCn-1 + ĀnBnCn-1 +

AnBnCn-1 + AnBnCn-1

Bn=AnBn+AnCn-1+BnCn-1

### Binary to Gray Code Table No.26

| B3,B2,B1,B0                           | G3,G2,G1,G0                   |

|---------------------------------------|-------------------------------|

| 0 0 0 0                               | 0 0 0 0                       |

| 0 0 0 1                               | 0 0 0 1                       |

| 0 0 1 0                               | 0 0 1 1                       |

| 0 0 1 1                               | 0 0 1 0                       |

| 0 1 0 0                               | 0 1 1 0                       |

| 0 1 0 1                               | 0 1 1 1                       |

| 0 - 1 - 1 - 0 - 6 - 1                 | 0 1 0 1                       |

| 0 1 1 1                               | 0 1 0 0                       |

| 1 0 0 0                               | 1 1 0 0                       |

| 10.0 1                                | 1 vo 1 vo 0 vo 1 vo 1 de 1    |

| o law O grillin Orang to white        | les acted to all and less and |

| laco de la languaga de la             | 1 teaching 1 at 0 temps       |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1 0 1 0                       |

| level wo at lead to become            | 1 0 1 1                       |

| 1 1 1 0                               | 1 0 0 1                       |

| 1111                                  | 1 0 0 0                       |

| 0.30.00                               | 181                           |

### **Gray to Binary Code Converter**

The simplified expression for binary code from gray code using K-Map is -

B3 = G3

B2 = G2 ⊕ G3

B1 =  $G1 \oplus G2 \oplus G3$

B0 =  $G0 \oplus G1 \oplus G2 \oplus G3$

### Procedure:

Set up gray to binary code converter using circuit given in figure no. 37. The circuit is using 3 EX-OR gate using IC 7486. Varify the binary code of respective gray code.

Page 15/31

Rev. 02

### Experiment -5 Study and Verification of Truth Tables of Comparator,

### Procedure

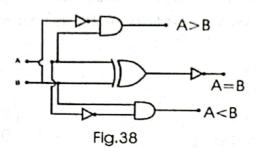

### One Bit Comparator

1. Truth Tables of One Bit Comparator.

| 7 | - |     | raune No. | •1                |

|---|---|-----|-----------|-------------------|

| A | В | A>B | A=B       | A <b< th=""></b<> |

| 0 | 0 | 0   | 1         | 0                 |

| 0 | 1 | 0   | 0         | 1                 |

| 1 | 0 | 1   | 0         | 0                 |

| 1 | 1 | 0   | 1         | 0                 |

The simplified expression for single bit comparator

### Procedure

Set up the circuit according to the fig.38. The operation can be performed through IC's 7486 (EX-OR) gate, 7404 (NOT **GATE) & 7408 (AND GATE)**

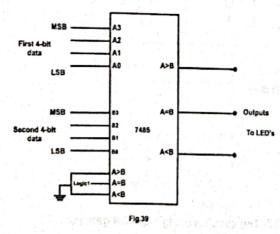

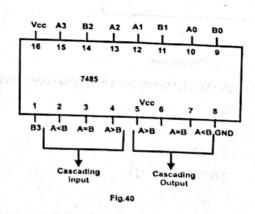

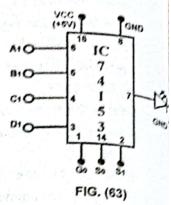

### 4-Bit Comparator

4-bit comparator are available in MSI (7485) which can be compare straight binaryand natural BCD codes, these ICs α be cascaded to compare words of greater lenghts without external gates. The A>B,A=B and A<B outputs of a stag handling less significant bits are connected to the corresponding A.B, A=B and a<B cascading inputs of the next stag handling more significant bits. The stage handling the least-significant bits must have A=B input connected to logic 1 levi and A>B and A<B inputs connected to logic 0 or 1 level. The pin description is shown in fig. 40.

Page 16/31 Rev. 02

Experiment - 6 Study of flip flops and verification of their truth tables.

Objective: Verification of D-type flip-flop (7474).

Theory: Delay flip flop or D type flip-flop is used to give delay of clock time to the input given signal. The D type flip-flop is used to divide the frequency of input square wave. Fig.41 shows a D type flip flop and truth table is given in Table No.28.

procedure

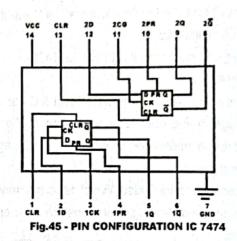

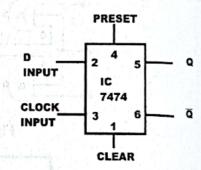

IC 7474 is a dual D-type positive edge triggered flip-flop. Pin configuration, circuit diagram and truth table are shown in Fig (45), (46) & table no.(30). D-type flip-flop has only one input referred to as D-input (Data Input). Make the circuit as shown in Fig. (46). Set Preset and Clear as giver in truth table, when clock is low, the flip-flop is latched in its last state. When clock is high the value od D-input is important. A high D-input sets the flip-flop, while a low D-input reset the flip-flop. Verify the truth table as given in table 30.

Fig. 41

Truth table of a D-type FLIP-FLOP

Objective -: Verification of J-K flip-flop (7476).

### **Procedure**

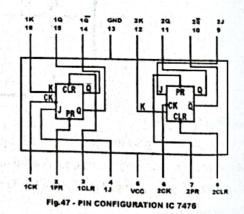

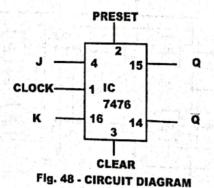

IC 7476 is a dual J-K flip-flop with Preset & Clear. Pin configuration, circuit diagram and truth table are shown in Fig (47), (48) & table no.31. This one input is negative edge reset (O). Again set it by using the PR terminal.

| Input       | Output<br>Qu+1 |

|-------------|----------------|

| D.          | 0              |

| Dia dixi ak | 1              |

In each case, observe Q also. Which is complement of Q. Verify that the presetting and clearing operations are independent of J & K inputs.

Basic Fig.

Fig.42

Fig.43

| Inputs |                | 1   | Output           |

|--------|----------------|-----|------------------|

|        | K <sub>n</sub> | N.  | Q <sub>n+1</sub> |

| 0      | 0              | H   | Q,               |

| 1      | 0              | 200 | 60. 1            |

| 0      | 1              |     | $\frac{0}{0}$    |

| 1 1    | 1              |     | Q <sub>n</sub>   |

### Flip Flop Operation

Set PR = CR = 1. Apply the clock manually by using a bounce a elimination switch and observe the output for all possible combinations of the inputs. Verify the truth table given in Fig. (47)

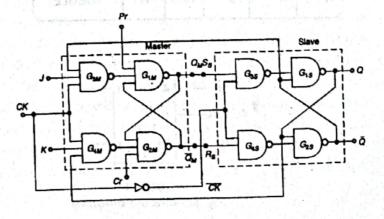

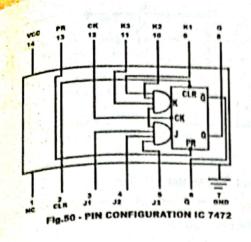

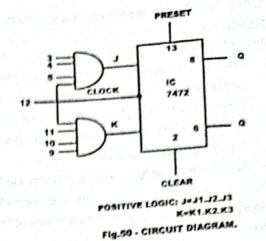

Object:-Verification of JK Master/ Slave flip-flop (7472). **Procedure**

For this flip-flop we are using IC 7472 JK Master/ Slave flip-flop with Preset and Clear. Pin configuration circuit diagram and truth table are

Fig.44

Page 17/31 Rev. 02

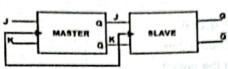

shown in Fig. (48), (49) & (50). In JK Master/ Slave flip-flop two JK flip-flop are connected by invert clock as shown in Fig. (44). The Master is positive-edge-triggered and the Slave is negative-

edge-triggered. Therefore, the master responds to its J and K control inputs before the slave. If J = 1, the master sets opositive clock edge. The high Q out of the master drives the J input of the slave. So, when the negative clock edge hits, the slave sets, copying the action of the master. If K = 1, the master resets on the leading edge of the clock. The high Q out, the master goes to the K input of the salve. Therefore, the arrival of the clock's trailling edge forces the slave to rese Again, the slave has copied the master. If the master's J and K inputs are high, it toggles on the positive clock edge and the slave toggles on the negative clock edge.

No matter what the master does, the slave copies it. If the master sets, the slave sets, if the master resets, if the master resets is the slave resets and the master resets and the slave resets and the

**TRUTH TABLE 29**

| INPL | JTS       | OUTPUTS  |   |    |    |

|------|-----------|----------|---|----|----|

| PRE  | CLE<br>AR | CK       | D | Q  | ā  |

| L    | Н         | X        | X | Н  | L  |

| н    | L,        | <b>X</b> | x | L  | H  |

| L    | L         | X        | x | н  | н  |

| н    | н         | 1        | н | Н  | L  |

| н    | н         | 1        | L | L  | н  |

| н    | н         | L        | x | Qo | Qo |

**TRUTH TABLE 30**

| IN                                  | PUTS | 11/11 |   | OUT   | PUTS       |    |

|-------------------------------------|------|-------|---|-------|------------|----|

| PRE                                 | CLE  | CLO   | J | K     | Q          | Q  |

| SET                                 | AR   | СК    |   | 11.00 |            |    |

| L                                   | н    | X     | X | X     | H          | L  |

| Н                                   | L    | x     | x | x     | L          | н  |

| L                                   | L    | X     | x | X     | н          | Н  |

| Н                                   | н    | Ω     | L | L     | Qo         | Qo |

| Н                                   | н    | Ω     | н | L     | н          | L  |

| $\mathbf{H}^{-1} = \mathbf{H}^{-1}$ | н    | Ω     | L | H     | See Langue | Н  |

| Н                                   | Н    | Ω     | Н | н     | TOGGLE     |    |

Fig. 46 - CIRCUIT DIAGRAM

Fig. 51 - MASTER/SLAVE FLIP-FLOP

**TRUTH TABLE -31**

| 1 30 -3 | NPUTS  |        | r je, flati | B 201 | OUTP | UTS |

|---------|--------|--------|-------------|-------|------|-----|

| PRESET  | CLEAR  | SCLOCK | J           | K     | a    | Q   |

| PRESET  | Н      | X      | X           | X     | Н    | L   |

| н       |        | X      | x           | x     | L    | Н   |

| A 18 6  | of Art | X      | x           | X     | Н    | Н   |

|         | н      | w      | L           | L     | Qo   | Q   |

| Н       | н      | w      | н           | L     | Н    | L   |

| Н       | H      | w      | L           | Н     | L    | Н   |

| н       | н      | w      | н           | н     | TOG  | GLE |

## Experiment 7 Study of Counters & Shift Registers and verification of their truth tables.

A counter driven by a clock can be used to count the no. of clock pulses. There are basically 2 different types of counters.

Synchronous Counter (Parallel

Here we have used ripple counter which is simple and straight forward in operation & construction and usually requires a minimum of hardware. Here each flip-flop is triggered by the previous flip-flop, which is why it is also called as a serial counter. For the 4 bit ripple counter, we have used two 7476 IC's each comprises of two flip-flops. For up counting, counter counts the no. of clock transition up to a maximum of 15. Clock pulses are applied at the clock input of first flip-flop & output of first flip-flop; i.e. QA is used to drive flip-flop B & QB is used to drive flip-flop C and so on. The counter begins at count 0000 & advances one count for each clock transition until it reaches count 1111. At this point, it resets back to 0000 & begains the count cycle all over again. For down counting, clock pulses are applied at the clock input of first flip-flop & compliment of QA is used to drive flip-flop B & QB is used to drive flip-flop C & so on. The counter begins at count 1111 & counter contents are reduced by one count with each clock transition until it counts 0000. At this point, it resets back to 1111 & begins the counts cycle all over again.

Page 19/31 Rev. 02

### Objective-4 Bit Binary Asynchronous Counters

### Procedure

### A. Forward Counter

Connect the circuit as shown in Fig. (52) by connecting clock output to ck input of first flip flop, connect Q1 to ck2,Q2 to ck3,Q3 to ck4. Also connect Q1, Q2, Q3 & Q4 to LED indicators.

Connect reset points of all the flip

flops & keep one lead open to connect it to ground point to reset the counter to 0000.

Conclusion:- counter counts the pulses up to decimel 15 & then on the application of next pulse, resets to zero automatic

DESET

The binary counter advances one bit each time at the trailing edge of the clock pulse.

### B. Reverse Counter:-

- Connect the circuit as shown in Fig. (53). 1.

- Connect preset of all flip-flops to one another. 2.

- Reset the flip-flop by connecting the preset 3. input i.e. PR to the ground momentarily. Observe that output at all the indicators are low (i.e. all the LED's are in OFF conditions).

- Apply clock pulses one by one using pulser 4. switch. Note all the four output's at each pulse & verify it with the table no. 33.

RESET FIG. (53) REVERSE COUNTER

FIG. (52) FORWARD COUNTER

Draw a graph of the output wave form with respect to the input pulses. 5.

TRUTH TABLE - 32

TRUTH TABLE - 33

| INPUT         |    |       |        |            |  |  |

|---------------|----|-------|--------|------------|--|--|

| Clock         | QD | QC ,  | QB     | QA         |  |  |

| 0             | 0  | 0     | 0      | 0          |  |  |

| 1             | 0  | 0     | 0      | 1          |  |  |

| 2             | 0  | 0     | 1      | 0          |  |  |

| 3             | 0  | 0     | 1      | 1.         |  |  |

| 4             | 0  | 1 Car | 0      | 0          |  |  |

| 5             | 0  | 1     | 0      | 1          |  |  |

| 6             | 0  | 1 1   | 1      | 0          |  |  |

| n ee <b>7</b> | 0  | 139   | a 1- 1 | 2 1 1 1 1  |  |  |

| 8             | 1  | 0     | 0      | 0          |  |  |

| 9             | 1  | 0     | 0      | 1          |  |  |

| 10            | 1  | 0     | 1      | 0          |  |  |

| 11            | 1  | 0     | 1      | 1          |  |  |

| 12            | 1  | 1     | 0      | 0          |  |  |

| 13            | 1  | 1     | 0      | iva njerio |  |  |

| 14            | 1  | 1     | JF 400 | 0          |  |  |

| 15            | 1  | 10    | 1100   | ed tapai.  |  |  |

| INPUT      | OUTPUT   |    |    |     |  |

|------------|----------|----|----|-----|--|

| Clock      | QD       | QC | QB | QA  |  |

| 0          | , 1      | 1  | 1  | 1   |  |

| 1          | 1        | 1  | 1  | 0   |  |

| 2          | 1        | 1  | 0  | 1   |  |

| 3          | 1        | 1  | 0  | 0   |  |

| 4          | 1.446    | 0  | 1  | 1   |  |

| 5          | 1        | 0  | 1  | 0   |  |

| 6          | 1        | 0  | 0  | 1   |  |

| 5 27 stf f | :: 1; :: | 0  | 0  | 0   |  |

| 8          | 0        | 1  | 1  | 1   |  |

| 9          | 0        | 1. | 1  | 0   |  |

| 10         | 0        | 1  | 0  | 1   |  |

| 11         | 0        | 1  | 0  | 0   |  |

| 12         | 0        | 0  | 1  | 1   |  |

| 13         | 0        | 0  | 1  | 0   |  |

| 14         | 0        | 0  | 0  | 1 1 |  |

| 15         | 0        | 0  | 0  | o   |  |

### C. Module Counter

### Theory

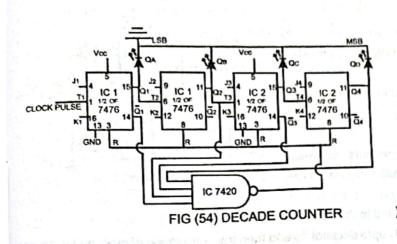

4 bit ripple counter counts upto 15 & then resets to '0'. But it can be made to reset at any clock pulse. For this purpos we operate the reset connections automatically using 4-input NAND GATE. As you know that output of a NAND GATE low if & only if all the inputs are high. Suppose we want to convert 4-bit forward counter to Decade counter. For Decade counter it is required that counter should count upto 9 & than resets to zero at tenth clock pulse. We know that at 10th clock pulse output of 2nd & 4th flip flop is high& output of 1st & 3rd flip flop is low. So we choose Q output of 2nd & 4th flip flop & Q output of 1st & 3rd flip flop for the inputs of 4-input NAND GATE. Also connect output of NAND GATE to common reset of all the flip flops. As you can program the counter for any number of Pulses.

| INPUT       | OUTPUT |    |    |    |  |  |

|-------------|--------|----|----|----|--|--|

| Clock       | QD     | QC | QB | QA |  |  |

| 0           | 0      | 0  | 0  | 0  |  |  |

| 1010        | 0      | 0  | 0  | 1  |  |  |

| 2           | 0      | 0  | 1  | 0  |  |  |

| 3           | 0      | 0  | 1  | 1  |  |  |

| 4           | 0      | 1  | 0  | 0  |  |  |

| 5           | 0      | 1  | 0  | 1  |  |  |

| 6           | 0      | 1  | 1  | 0  |  |  |

| 7           | 0      | 1  | 1  | 1  |  |  |

| 8           | 1      | 0  | 0  | 0  |  |  |

| (00 rgorica | 1 1    | 0  | 0  | 1  |  |  |

| 10          | 0      | 0  | 0  | 0  |  |  |

**TRUTH TABLE - 34**

### **Excess 3 Counter**

This is another form 8 BCD code, in which each decimal digit 13 coded into a 4 bit binary code. The code for each decimal digit 13 obtained by adding decimal 3 to the natural BCD code of the digit . For example decimal 5 is coded as 0101 + 0011=1000 in excess 3 code.

An excess 3 counter can be made by converting the updown counter to its excess- 3code.

For Ex. using IC's 74193 (Asynchronous up down counter) output up counter add binary three in the 4 bit adder

## Objective- 4 Bit up Down Binary Synchronous Counter

### Theory

A counter is sequential logic circuit made up of flip flops and is used to count the number of pulses apply to it. The input pulse change the status of the flip flops in such a way that by observing the output levels, the total number of input pulses applied can be determined. The ripple counter is simplest to build, but there is a limit to its highest operating frequency. Each flip flop has a delay time. In a ripple counter these delay times are additive and the total settling time for the counter is approximately delay time times the total number of flip flops. This speed limitation can be overcome by the use of a synchronous or parallel counter. The difference here is every flip flop is triggered by the clock. If the asynchronous operation of a counter is changed so that all flip flops are clocked simultaneously (synchronously) by the input pulses, the propagation delay time may be reduced considerably. Repetition rate is limit by the delay of anyone flip flop plus the propagation time of any control GATE required.

Typically, the maximum frequency of operation of a 4-bit synchronous counter using TTL logic is 32MHz, which is about twice that of a ripple counter, another advantage of the synchronous counter is that no decoding spikes appear at the output since all flip flops change state at the same time. Hence the strobe pulse is required when decoding a synchronous counter.

### **Procedure**

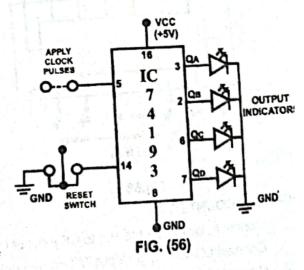

### Up (Forward) Counter

- 1. Connect the circuit as shown in Fig.56.

- 2. Switch ON the instrument using ON/OFF toggle switch provided on front panel.

- 3. Press push to OFF reset switch once to reset the output at logic 0000.

- 4. Apply clock pulses one by one using pulser switch. Note down the status of all the four outputs at each applying pulse and compare the results with truth table no.(1).[as in case of asynchronous up counter) 5.

- Draw a graph of the output wave from with respect to the input pulses.

Conclusion: - Counter counts the pulses from 0000(1) upto decimal 15 and then the application of next pulse, resets to zero automatically. The binary counter advances one bit each time at the tariling edge of the clock pulse. Down (Reverse) Counter :-

- 1. Connect the circuit as shown in fig.57 given above.

- 2. Switch ON the instrument using ON/OFF toggle switch provided on front panel. 3.

- Press push to ON reset switch once to reset the output of logic 0000. 4.

- Apply clock pulses one by one using pulser switch. Note down the status of all the four outputs all each applying pulse and compare the results with Truth Table no.(2). [as in case of asynchronous down counter]. 5.

- Draw a graph of the output wave from with respect to the input pulses.

Conclusion :- Counter counts the pulses from 1111 (decimal 15) upto 0000 (decimal 0) and then the application of next pulse, resets to 1111 automatically. The binary counter advances one bit each time at the tariling edge of the clock pulse.

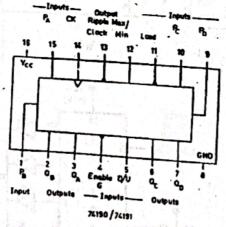

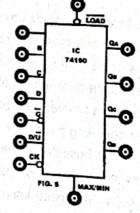

All counters in 74190 are fully programmable . The counter can be preset to any desired BCD digit as determined by the

Fig.58

VCC (+5V)

OUTPUT

NDICATORS

GND

IC

7

4

1

3

GND

FIG. (57)

APPLY CLOCK PULSES

Fig.59

### **DECADE UP COUNTER**

- Connect clock output (1 Hz) to CK input of the IC 74190 through single point patch cords. 1. 2.

- Connect LOAD to logic input '0' ( ground point) and also D/U pins to ground point . Apply logic 0 on 3.

- Connect 4 logic outputs to output indicators.

- Apply logic 1 on LOAD pin of IC. 5.

Page 22/31 Rev. 02 Apply clock pulses one by one using pulser switch. Note down all the four outputs at the application of each pulse & verify the truth table.

conclusion: Counter counts the pulses up to 9 i.e. from 0000 to 1001and then on the application of next pulse, reset 0000 automatically.

## Decade Down Counter

Apply logic 1 to D/U pin of IC

Apply clock pulses one by one using pulser swithc. Note down all the four outputs at the application of each pulse and verify that the counter counts from 1001 to 0000 and then on application of next pulse, reset to 0000 automatically.

### objective-Study of SHIFT Register

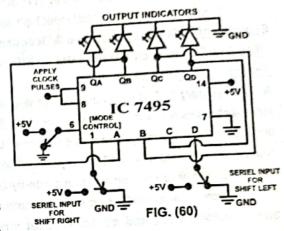

### Serial to Parallel and Parallelto Serial SHIFT Register using IC 7495

### Theory

A SHIFT register is basically a storage medium where one or more binary words may be stored. Like a counter, it is also made up of binary storage elements, usually flip-flops. These elements are cascaded in such a way that the bit stored there can be moved or shifted from one element to another adjacent element. All of the storage registers are activated simultaneously by a single input 'CLOCK' or 'SHIFT' pulse. When a shift pulse is applied, the data stored in the shift register is moved one position either to left or to right as

desired. Because of its ability to move the data, one bit at a time, the SHIFT Register is valuable in performing a wide variety of logic operations like counting, frequency dividing or performing airthmatic operations. The storage capacity of a SHIFT Register depends on the number of

binary elements used. Most SHIFT Register operations are serial operations, but many circuits are provided with parallel inputs and parallel outputs such SHIFT Registers permit data to be preset in parallel and data to be readout in parallel. This property makes the SHIFT Register an ideal circuit for performing serial to parallel and parallel to serial conversions.

SHIFT Registers can also be used to perform arithmatic operations. Shifting the data stored in a SHIFT Register, to the right or to the left by one bit is equivalent to multiplying or dividing that number by two. In addition, SHIFT Registers can also be used for generating a sequence of control pulses for a logic circuit. In some applications, SHIFT Registers are used for counting and frequency division.

### Procedure for Serial to Parallel SHIFT Register

- Connect the circuit as shown in Fig. (60).

- 2. Switch ON the instrument using ON/ OFF toggle switch provided on front panel.

- Put the mode control switch to ground i.e. 0 volt to enable the IC perform right SHIFT operation.

- Put serial input and D input to ground. Apply four clock pulses and record the final output state as below

ABCD = \_\_\_\_\_\_

- 5. Put serial input to +5V. Apply four clock pulses again and record the final outputs in the same manner. Note the direction in which the

- C PULSES 9 QA QB QC QD A S IC 7495

REV 6 CONTROL 7 GND

THE FIG. (61)

- data shifts.

6. Set serial input to ground. Apply four clock pulses and note the direction in which the data shifts.

- Put mode control switch to +5V. Also put the D input to +5V. Apply SHIFT pulses and note down the direction of shifting. Record the final state after four pulses.

Page 23/31 Rev. 02 Set D input to binary 0 i.e. to ground. Apply two shift pulses and record the contents of the register in the sa

### Procedure for Parallel to Serial SHIFT Register

- 1. Connect the circuit as shown in Fig. (61).

- Switch ON the instrument using ON-OFF toggle switch provided on front panel. 2.

- 3.

- Put mode control switch to +5V and apply one clock pulse. Note output levels and record the observations 4 Set the Data inputs A B C and D to +5 V. Apply one clock pulse and record the observations in the same management and note the

- 5

- Put mode control input to ground. Apply four clock pulses one by one and note the 6. outputs each time.

Note :- Any parallel data from 0000 to 1111 at inputs A B C and D can be loaded into the SHIFT Register keeping the mode control input high and applying a clock pulse.

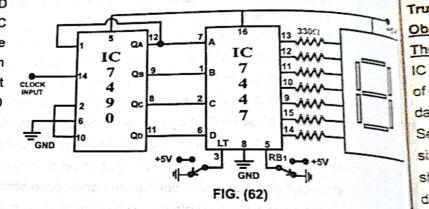

Experiment -8 Study of Encoders & Decoders and verification of their truth tables.

### Objective-Decimal to BCD Encoder & BCD TO 7-Segment Decoder

### Theory

A BCD (Binary coded decimal) counter is a sequential circuit that counts by tens. It has ten discrete states which represent decimal numbers from 0 through 9. Because of its ten state nature, A BCD counter is also referred to as

decade counter. The integrated circuit 7490 is a BCD counter using the standard 8421 binary code. The IC consists of one divide by -two and one divide-by-five circuit, which are independent except for a common power supply input and common reset input terminals. In addition to counting circuits, the 7490 also contains two numbers of 2-input NAND GATES. A low input to at least one input of each GATE is necessary to enable counting. If both inputs to GATES G1 and G2 are high, the counter is reset to binary 0000. These inputs are marked as Ro(1) and

Ro (2). On the other hand, if both inputs to gates G3 and G4 go high, the counter is reset to binary 1001 (decimal 9). These inputs are marked as R9 (1) and R2.

A BCD to 7-segment decoder circuits 7447 is a special form of decoder circuit that accept the standard 8421 BCD input code and generate a special 7-bit output code that is used to operate a 7-segment readout. The output transistors in 7447 can stand upto 15v. It can sink enough current to drive common anode type LED 7-segment displays directly. In addition to BCD inputs and seven outputs for driving segments, the IC have a lamp test input, a blanking input/ripple blanking ouput and a ripple blanking input.

### Procedure:

### Verification of Decimal to BCD Encoder :-

- Connect the circuit as shown in Fig. (62). 1.

- 2. Put Ro to ground and R9 to +5v. Note the output levels. 3.

- Put R0 to +5v and R9 to ground. Note the output levels. 4.

- Put both R0 and R9 to ground. Apply clock pulses one by one and note the output levels when the clock pulse goes high and when it goes low.

- Repeat step 4 above for about 20 clock pulse. 5. 6.

- Tabulate your observations as shown in truth table.

- Draw output waveforms with reference to the clock pulse

Page 24/3

6.

## verification of BCD to decimal decoder

- Connect the circuit as shown in Fig. (62).

- Switch ON the instrument using ON/ OFF toggle switch provided on front panel. The seven segment display shows any arbitrary Fig.

- Connect lamp-test (LT) of IC 7447 to 3. ground. All LED segments should light up showing a Fig. 8.

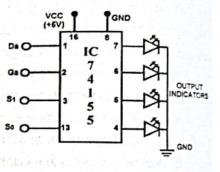

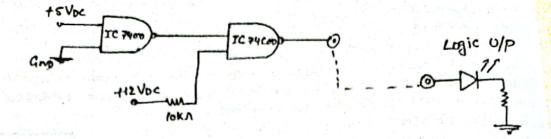

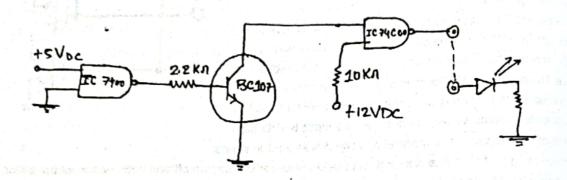

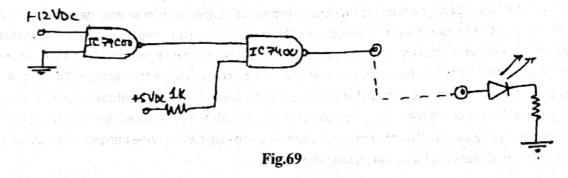

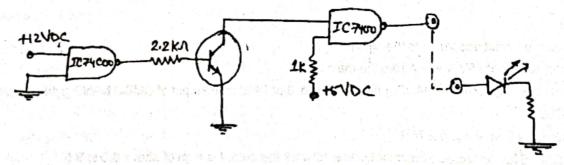

- Make lamp test input high. Apply clock 4. pulses one by one and see that the figures displayed by the LED repeat sequentially from 0 through 9.